반도체 제조 공정

|

|

성장된 규소봉을 균일한 두께의 얇은 웨이퍼로 잘라낸다. 웨이퍼의 크그는 규소봉의 구경에 따라 3",4",6",8"로 만들어지며 생산성향상을 위해 점점 대구경화 경행을 보이고 있음 |

|

|

|

|

CAD(Computer Aided Design)시스템을 사용하여 전자회로와 실제 웨이퍼 위에 그려질 회로패턴을 설계한다. |

|

|

|

|

|

설계된 회로패턴을 E-beam설비로 유리판 위에 그려 MASK(RETICLE)를 만듬. |

|

|

|

|

|

고온(800~1200℃)에서 산소나 수증기를 실리콘 웨이퍼표면과 화학반응시켜 얇고 균일한 실리콘산화막(SiO2)를 현상시켜는 공정 |

|

|

|

|

빛에 민감한 물질인 PR를 웨이퍼 표면에 고르게 도포시킴 |

|

|

|

|

|

STEPPEE를 사용하여 MASK에 그려진 회로패턴에 빛을 통과시켜 PR막이 형성된 웨이퍼 위에 회로패턴을 사진 찍는 공정 |

|

|

|

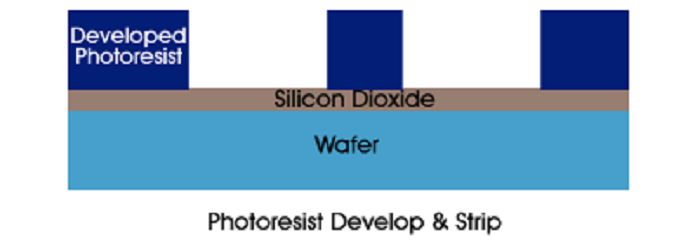

웨이퍼 표면에서 빛을 받은 부분의 막을 현상시키는 공정 (일반 사진현상과 동일) |

|

|

|

|

|

회로패턴을 형성시켜 주기 위해 화학물질이나 반응성 GAS를 사용하여 필요없는 부분을 선택적으로 제거시키는 공정 이러한 패턴형성과정은 각 패턴층에 대해 계속적으로 반복됨 |

|

|

|

|

|

METAL ETCT

|

|

회로패턴과 연결된 부분에 불순물을 미세한 GAS입자 형태로 가속하여 웨이퍼의 내부에 침투시킴으로써 전자소자의 특성을 만들어 줌 이러한 불순물주입은 고온의 전기로 속에서 불순물입자를 웨이퍼 내부로 확산시켜 주입하는 DIFFUSION(확산)공정에 의해서도 이루어짐 |

|

|

|

|

|

|

12단계 화학기상증착(CVD:Chemical Vapor Deposition)공정 GAS간의 화학반응으로 형성된 입자들을 웨이퍼표면에 증착하여 절연막이나 전도성막을 형성시키는 공정 |

|

|

|

|

|

웨이퍼 표면에 형성된 각 회로를 알루미늄선으로 연결시키는 공정 |

|

|

|

|

웨이퍼에 형성된 IC칩들의 전기적 동작여부를 컴퓨터로 검사하여 불량품을 자동선별하는 공정 |

|

|

|

|

웨이퍼상의 수 많은 칩들을 분리하기 위해 다이아몬드 톱을 사용하여 웨이퍼를 전달하는 공정 |

|

|

|

|

낱개로 분리되어 있는 칩 중 EDS TEST에서 실품으로 판정된 칩을 리드프레임(READ FRAME)위에 올려놓은 공정 |

|

|

|

|

칩 내부의 외부연결단자와 리드프레임을 가는 금선으로 연결하여 주는 공정 |

|

|

|

|

|

연결 금선 부분을 보호하기 위해 화학수지로 밀봉해 주는 공정 |

|

|

|

성형된 칩의 전기적 특성 및 기능을 컴퓨터로 최종검사하는 공정으로 최종 합격된 제품들은 제품명과 회사명을 MARKING한 후 입고 검사를 거쳐 최종소비자에게 판매된다. |

|

|

|